## Devices with electrically tunable topological insulating phases

## Paolo Michetti<sup>1</sup> and Björn Trauzettel<sup>1</sup>

<sup>1</sup>Institute for Theoretical Physics and Astrophsics, University of Würzburg, Am Hubland 97074 Würzburg

Topological insulators (TIs) are time-reversal symmetric phases characterized by a topological  $Z_2$  invariant. The boundary between a normal and a topological insulator is signaled by the appearance of helical edge modes, with spin-momentum locking, where transport is topologically protected against the scattering on non-magnetic disorder. Solid-state topological insulating phases promise, therefore, a powerful route for spin and charge manipulation in electronic devices.

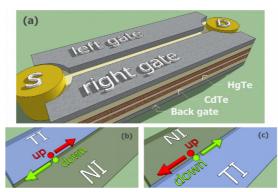

While a possible choice to control transport in the edge modes is through quantum interference, we argue that a most straightforward implementation of a device requires a material with an easily tunable TI phase. We focus on a HgTe/CdTe double quantum well device and show that a topological phase transition can be driven by an inter-layer bias voltage [1], even when the individual layers are non-inverted. This paves the way to the realization of tunable topological mass domains of desired shape using lithographic gates. Helical edge modes located on such domain lines [2] can therefore be easily manipulated.

We then introduce the concept of a topological field-effect-transistor [3], where charge and spin transport in the helical edge modes is controlled by electrically switching the TI phase. We analyze further application to a spin battery [3], which also realizes a set up for an all-electrical investigation of the spin-polarization dynamics in metallic islands.

- [1] P. Michetti, J. C. Budich, E. G. Novik and P. Recher, Phys. Rev. B 85 (2012) 125309.

- [2] P. Michetti, P. H. Penteado, J.C. Egues and P. Recher, Semicond. Sci. Technol. 27 (2012) 124007.

- [3] P. Michetti and B. Trauzettel, Appl. Phys. Lett. 102 (2013) 063503.

Fig. 1: Isometric sketch of a HgTe/CdTe DQW device with a back gate and two distinct top gates (left and right). In the ON state, top gates induce a gate-bias domain leading to a TI/NI interface (channel) where helical edge modes are found. Source (S) and drain (D) leads, placed along the interface between L and R top gates, collect charges from the edge modes. The lateral surface of the DQW is specifically treated to ensure negligible edge transport. (b) Schematic description of a TI/NI interface for direct gate polarization with indication of the helical spin transport of edge states. (c) Reverse gate polarization leading to opposite spin transport of the channel.